三星电子代工业务总裁Si-young Choi在三星晶圆代工论坛作主旨演讲

在5nm以下制程领域中,仅剩下了三星和台积电最后两家企业,但这两家企业的竞争仍十分激烈,你来我往,形成了拉锯战。而正是这样的拉锯战,促使摩尔定律在重重困难之下,仍不断按照一定速度向前延伸。

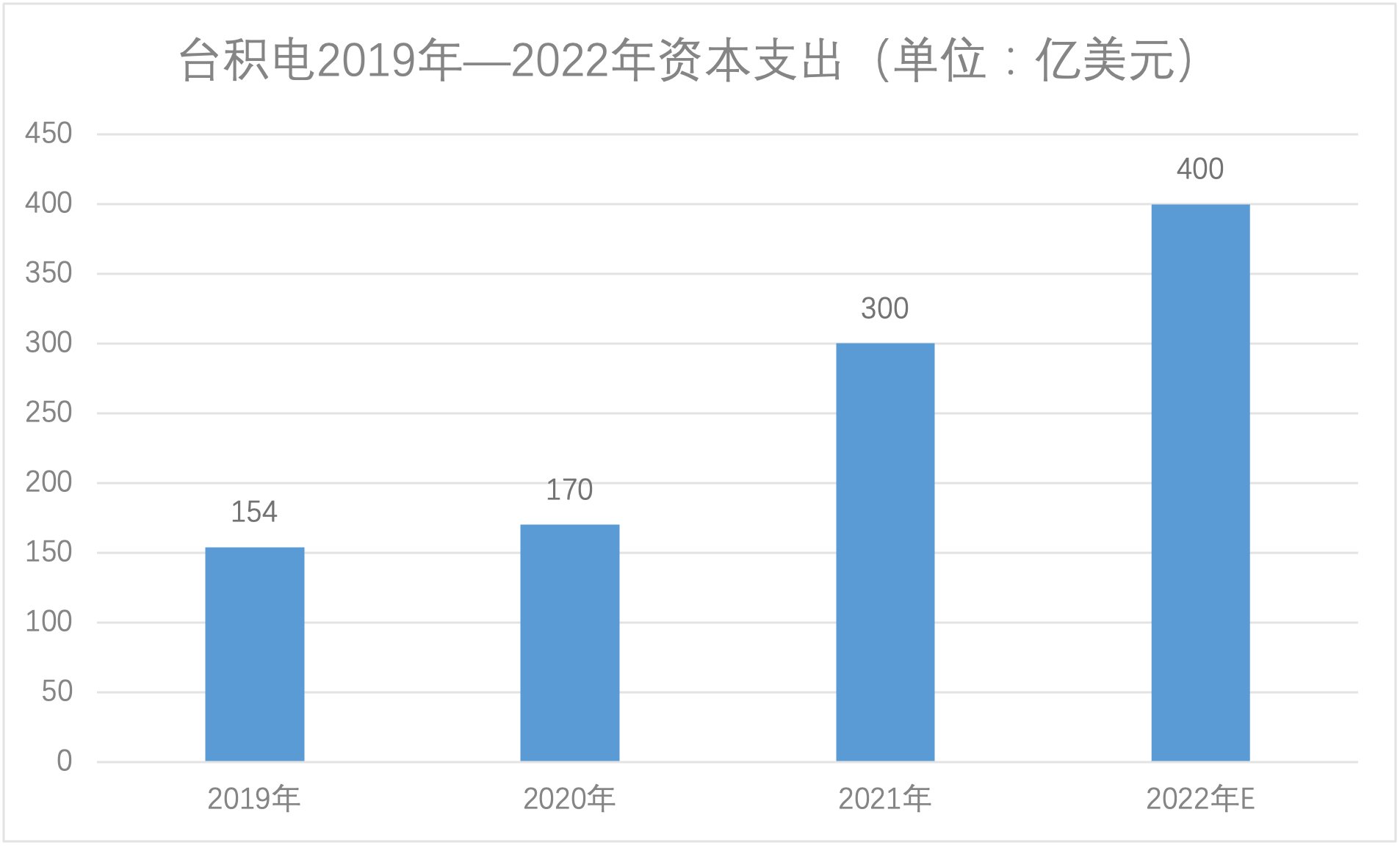

资本支出是先进制程拉锯战的底气

在5nm以下先进制程领域,为何台积电、三星这两家企业能“笑”到最后?甚至还能在如此艰难的先进制程领域打起拉锯战?

根据DIGITIMES数据评估,28nm工艺建厂花费为60亿美元(约合人民币382亿元)。然而到7nm工艺时,建厂成本却增长至120多亿美元(约合人民币765亿元)。到5nm时,这一数字更是增长至160亿美元(约合人民币1019亿元)。可见,晶圆厂的建设成本十分高昂,且随着芯片制程的逐渐缩小不断攀升。对于5nm以下的先进制程芯片而言,成本更加高昂。

面对如此“砸钱”的买卖,三星、台积电也展示出了强大的资金实力。IC insights的数据显示,2021年半导体行业资本支出合计为1520亿美元,三星电子和台积电的资本支出合计超过了600亿美元,占总资本支出的近40%。

在今年6月8日举办的股东大会上,台积电董事长刘德音预计,明年台积电资本支出会达到400亿美元。如果按此速度继续增长,将意味着台积电2021—2023年的资本支出极有可能超过此前宣布的3年千亿美元,达到1100亿美元~1140亿美元之间(约合7391亿~7660亿人民币)。

台积电2019年—2022年资本支出(数据来源:根据公开资料整理)

此外,Counterpoint称,台积电高额的资本支出将有很大一部分是对3nm和2nm节点产能的扩建,因为英特尔和苹果等大客户在2023年后对先进制程的需求比较大。

在代工方面的资本支出,三星也毫不逊色。2021年,三星电子半导体与显示总资本支出达48.22万亿韩元(约合2500亿人民币),其中用于半导体的有43.57万亿韩元(约合2300亿人民币),其资金主要集中用于产能扩张和先进节点的迁移。今年5月,三星电子宣布未来5年重大投资计划中表示,在2026年前,将资本支出增加30%以上,达450万亿韩元(约合2.4万亿人民币)。虽然三星电子没有透露各业务的支持占比,但有分析师初步预测,其在半导体领域将支出超千亿美元。

业内专家莫大康向《中国电子报》记者表示,三星多年来在存储器领域独占鳌头,有足够的资本投入在先进制程的研发中。“虽然对于三星而言,代工行业并不是其营收的‘主力军’,与台积电相比,其代工领域一年的营收只有台积电的1/3,但三星作为全球龙头IDM厂商,且拥有雄厚的资金支持,追求先进制程也意味着追求市场的话语权,这也是三星能不断在先进制程领域‘砸钱’并与台积电不断抗衡的主要原因之一。”莫大康说。

强大的资本支出能力,也给了三星、台积电足够的底气,使其能够在先进制程领域你来我往。

四大核心技术成竞争焦点

台积电、三星在先进制程的拉锯战中,主要围绕四大核心技术展开竞争。

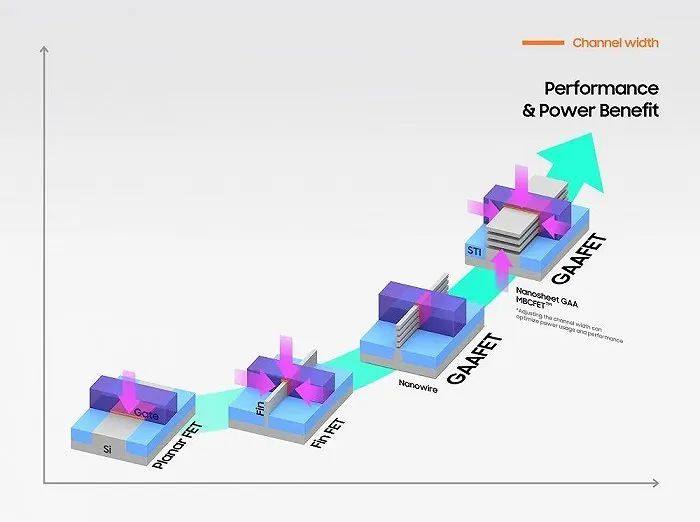

其一,晶体管结构。据了解,随着芯片制程延伸到5nm以下,原本采用的三面围栅的FinFET晶体管结构开始出现漏电流所导致的功耗与发热问题,这也使得采用四面环栅结构的GAA技术逐渐受到更多关注。复旦大学微电子学院副院长周鹏表示,相较于三面围栅的FinFET结构,GAA技术的四面环栅结构可以更好地抑制漏电流的形成以及增大驱动电流,进而更有利于实现性能和功耗之间的平衡。因此,GAA技术在5nm之后更小的制程中,更受到业界的认可和青睐。

在晶体管结构方面,三星先台积电一步,在其3nm芯片中便开始采用GAA架构,还与IBM联合推出了一种新的垂直晶体管架构VTFET。据了解,在同等功率下,VTFET晶体管提供了FinFET晶体管2倍的性能,而在等效频率下,VTFET可以节省85%的功率。此外,台积电也在GAA架构中不断有所建树,在去年12月的中国集成电路设计业2021年年会上,台积电(中国)总经理罗振球称,台积电将在2nm节点中采用基于GAA架构的MBCFET晶体管架构。

三星电子晶体管结构路线图(来源:三星电子)

其二,新材料。为了解决晶体管微缩后带来的量子效应、漏电发热等问题,并有效提升芯片能耗、减小芯片面积,台积电、三星等厂商开始不断寻找能够在先进制程芯片中替代或者补充硅材料不足的新材料。据了解,台积电正在研究二硫化钨(WuS2)和碳纳米管等新材料,这些材料能够更有效地移动电子,并让芯片在计算过程中更加节能,降低功耗。此外,三星电子也与蔚山科技学院合作开发出新材料“非晶氮化硼(a-BN)”。据悉,该材料能够起到阻止电干扰的作用,三星将其视为半导体小型化的关键元素之一。

其三,新的光刻设备。下一代EUV光刻机可谓是攻破2nm以下先进制程的命脉,因此,三星、台积电均开始奋力寻求ASML高数值孔径极紫外光刻机。今年6月17日,台积电举行的技术论坛上首次披露,到2024年台积电将拥有ASML最先进的高数值孔径极紫外光刻机,用于生产GAA架构的2nm芯片,并预计在2025年量产。据了解,高数值孔径极紫外光刻机具备更高的光刻分辨率,能够将芯片体积缩小的同时,密度增加2.9倍。几乎同一时间,有报道称三星电子从ASML获得了十多台EUV光刻机,且三星同样表示其2nm芯片将于2025年量产,可见这几台光刻机也在为2nm芯片的量产做准备。

其四,先进封装技术。随着芯片制程的演进和晶体管结构的改变,如何能将芯片“封”得更小,并实现更优质的互联也成为台积电、三星的主攻点。因此,近年来,台积电也在先进封装领域不断发力,接连推出了CoWoS、SOIC 3D等技术,完善其在先进封装领域的布局。为了进一步扩大其在先进封装上影响,2020年台积电将其旗下SoIC、InFO及CoWoS 等3D IC技术平台进行了整合,并命名为3D Fabric。据台积电介绍,在产品设计方面,3D Fabric提供了最大的弹性,整合逻辑Chiplet、高带宽内存(HBM)、特殊制程芯片,可全方位实现各种创新产品设计。

尽管起步较晚,但三星近年来一直坚持不懈地研发先进封装技术。2021年11月,三星宣布已与AmkorTechnology联合开发出混合基板立方体(H-Cube)技术,这是其最新的2.5D封装解决方案,大大降低了高性能计算等市场的准入门槛,使得三星在先进封装领域名声大震。

拉锯战推动摩尔定律不断前行

如今,三星和台积电在先进制程领域的竞争已经进入了白热化阶段,也成为推动摩尔定律继续前行的主要动力之一。

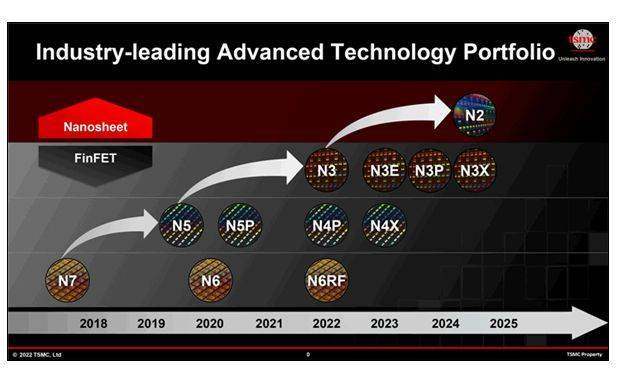

在这场拉锯战中,三星目前处于劣势,且先进制程芯片频频陷于良率的泥沼。据悉,三星4nm良率仅为35%,而台积电4nm制程工艺芯片的良率可达到70%,是三星的两倍。因为良率问题,三星晶圆代工的主要客户正在流失。例如,高通将骁龙8 Gen1订单转向台积电生产,后续3nm芯片也全量委托给台积电;英伟达RTX 40系列显卡也将采用台积电5nm制程。由于三星电子基于4nm制程的Exynos 2200处理器良率表现十分之低,其GPU频率从计划的1.69GHz削减到1.49GHz,最终减少到1.29GHz。为此,三星电子代工的大客户高通和英伟达已经协商按照芯片最终产量付费,而非按晶圆付费。

台积电在先进制程领域相对顺利。近期有消息称,尽管如今还未量产3nm工艺,台积电3nm良率已达80%,其最大的客户苹果,已经提前预定其M3芯片采用台积电3nm制程。甚至有消息称,台积电2nm的风险试产良率也已超过了90%,苹果和英特尔等巨头企业,也将作为台积电2nm的首批客户。

台积电先进制程演变路径

莫大康表示,台积电、三星之间的竞争也没有绝对的输赢之分,因为绝大部分晶圆代工厂商已经完全告别了先进制程的竞赛,使得诸多客户只能在台积电和三星之间进行“非此即彼”的选择,而台积电一家的产能,也难以维持庞大的先进制程市场。因此,哪怕三星的芯片会频频陷入性能“滑铁卢”的风险,也依旧会有大批厂商愿意去“尝尝螃蟹”。

这样的竞争态势,恰巧成为了推动摩尔定力继续前行的主要动力。“虽然,三星在产品良率以及客户订单量方面三星不如台积电,但是对于台积电而言,并不是无所顾忌。三星背后不可忽视的强大资本力量,是台积电最顾忌的方面之一。此外,正是因为三星追得紧,所以这也成为了敦促台积电不断向先进制程延伸的最大动力之一。二者的拉锯战,也成为了推动摩尔定力继续前行的动力。”莫大康表示。

网站导航

网站导航

相关文章

相关文章

精彩导读

精彩导读

热门资讯

热门资讯